Dimitrisvlamis

Member level 2

Greetings,

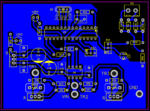

I am currently working in this circuit of an SPWM inverter and i keep having my mosfets buring after each time i conect the ceter tap to the transformer! I am running out of ideas, mosfets and...money haha :lol: The circuit is pretty simple. The code works, i tested it from arduino without mosfets. I generate spwm signals (no signal is on each other) with frequency of 50Hz and pwm frequency of 15000kz. My input is 12V and i use an iron transformer 8-0-8 to 220v taken from a UPS. Any sugestions why my mosfets burn?

I am currently working in this circuit of an SPWM inverter and i keep having my mosfets buring after each time i conect the ceter tap to the transformer! I am running out of ideas, mosfets and...money haha :lol: The circuit is pretty simple. The code works, i tested it from arduino without mosfets. I generate spwm signals (no signal is on each other) with frequency of 50Hz and pwm frequency of 15000kz. My input is 12V and i use an iron transformer 8-0-8 to 220v taken from a UPS. Any sugestions why my mosfets burn?