HiQureshi

Newbie level 6

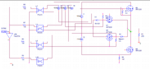

Even if I increase the capacitance of C1 and C2 upto 1000uF, the output remains the same.

Do you mean I have to increase the frequency of the gating signals or do you mean something else?

Do you mean I have to increase the frequency of the gating signals or do you mean something else?