Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

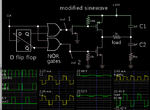

modified sine wave.

Also I want to ask, would it matter if the bidirectional switch is designed by using P-channel MOSFETs and the half bridge MOSFETs as N-channel (as opposed in the original figure given in previous post) ?

All four gate drivers are supplied by one power supply, so they surely don't provide isolated gate drive. I neither get the idea behind using multiple Arduinos. How should they generate synchronized waveforms? You need some kind of digital isolators, e.g. high speed opto couplers.

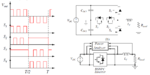

The P device is nearest the positive power supply. It turns on fully because it is driven by an N-device. It shuts off fully due to a pullup resistor to supply+.

The flip-flop and logic gates convert a single incoming clock signal into two correct bias drivers for the push-pull half-bridge.

Also notice my simulation has low supply voltage. It is wise to start with low voltage rather than jump immediately to full house voltage.

Yes apparently that is the goal for now.Can you confirm your goal is a normal modified sinewave?

This simulation creates a normal modified sinewave. It started with the section of your schematic (post #8) that does the conversion work, that is, the upper half.

The P device is nearest the positive power supply. It turns on fully because it is driven by an N-device. It shuts off fully due to a pullup resistor to supply+.

The flip-flop and logic gates convert a single incoming clock signal into two correct bias drivers for the push-pull half-bridge.

My schematic does not address all concepts of your project, since you're trying to obtain more complicated driving waveforms. Can you confirm your goal is a normal modified sinewave? Our intention is to guide people's projects and not to hand them a solution.

Also notice my simulation has low supply voltage. It is wise to start with low voltage rather than jump immediately to full house voltage.