CAMALEAO

Full Member level 4

Hi people,

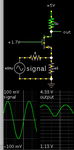

I have a question regarding the common-gate amplifier.

How can I setup a common gate amplifier with a current source as a bias? And what are the condition to check if it is in saturation?

Regards.

I have a question regarding the common-gate amplifier.

How can I setup a common gate amplifier with a current source as a bias? And what are the condition to check if it is in saturation?

Regards.