Vivek2Keviv

Newbie level 2

Hello all,

Greetings! Hope you all doing good!

I have a quick question about synopsys DC synthesis.

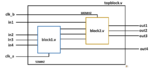

I have a top module called "topblock.v". This module has two sub modules called "block1.v", "block2.v".

The outputs of "block1.v" goes to "block2.v" as the inputs but the module "block1.v" is runnig with clock "clk_a" and the module "block2.v" is running with clock "clk_b".

Now the top module has two sub-modules running with two clocks!

I have a start up problem here.

1. Should I need to use TOPMODULE.v as design entry here? (TOPMODULE.v includes two submodules)?

2. I have used "set_clock groups" to seperate two clock group but I couldn't constraint the corresponding input,output delays.

3. Why I couldn't seperate inputs and outputs with respect to clocks?

4. I have the scripts below. Can anyone please let me know what is the problem with this script?

I also attached image to clarify the situation.

Thanks in advance.

Vivek.

Greetings! Hope you all doing good!

I have a quick question about synopsys DC synthesis.

I have a top module called "topblock.v". This module has two sub modules called "block1.v", "block2.v".

The outputs of "block1.v" goes to "block2.v" as the inputs but the module "block1.v" is runnig with clock "clk_a" and the module "block2.v" is running with clock "clk_b".

Now the top module has two sub-modules running with two clocks!

I have a start up problem here.

1. Should I need to use TOPMODULE.v as design entry here? (TOPMODULE.v includes two submodules)?

2. I have used "set_clock groups" to seperate two clock group but I couldn't constraint the corresponding input,output delays.

3. Why I couldn't seperate inputs and outputs with respect to clocks?

4. I have the scripts below. Can anyone please let me know what is the problem with this script?

I also attached image to clarify the situation.

Thanks in advance.

Vivek.

Code:

analyze -format verilog -library work TOPMODULE.v

elaborate TOPMODULE

create_clock -period 10 -name CLK_A [get_ports CLK_A]

create_clock -period 20 -name CLK_B [get_ports CLK_B]

set_clock_groups -asynchronous -group CLK_A -group CLK_B

report_clock

check_timing

set_clock_latency 1 [get_clocks CLK_A]

set_clock_uncertainty 0.3 [get_clocks CLK_A]

set_clock_transition -max 0.25 [get_clocks CLK_A]

set_clock_transition -min 0.04 [get_clocks CLK_A]

set_clock_latency 2 [get_clocks CLK_B]

set_clock_uncertainty 1 [get_clocks CLK_B]

set_clock_transition -max 0.4 [get_clocks CLK_B]

set_clock_transition -min 0.1 [get_clocks CLK_B]

report_clock -skew

check_timing

set_ideal_network [get_ports RESET]

set_input_delay 1 -max -clock CLK_A [remove_from_collection [all_inputs] [get_ports CLK_A]]

set_output_delay 1 -max -clock CLK_A [all_outputs]

set_input_delay 4 -max -clock CLK_B [remove_from_collection [all_inputs] [get_ports CLK_B]]

set_output_delay 3 -max -clock CLK_B [all_outputs]