chiques

Full Member level 3

- Joined

- Nov 21, 2007

- Messages

- 168

- Helped

- 2

- Reputation

- 4

- Reaction score

- 2

- Trophy points

- 1,298

- Location

- California

- Activity points

- 2,534

Hello Everyone,

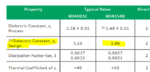

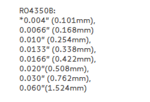

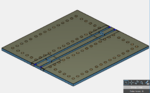

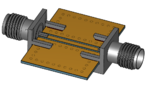

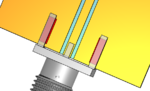

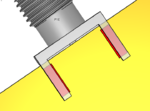

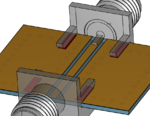

I calculated a CPW using Avago’s AppCad. My parameters are:

Εr=3.48

Substrate Thickness=24 mils

Trace Width = 50 mils

Gap=20.5 mils

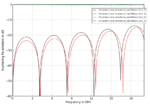

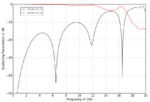

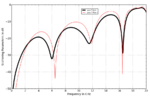

I build this board and it turns out my transmission and reflection begins to deteriorate really bad after 6 GHz.

I also simulated this on a 3D EM simulator. This also shows both my S11 and S21 are poorly performing.

As a sanity check I made the trace thinner (down to 10 mil) and it significantly improved both S11 and S21.

Does anyone have any idea what I’m doing wrong?:?::?::?::?:

I calculated a CPW using Avago’s AppCad. My parameters are:

Εr=3.48

Substrate Thickness=24 mils

Trace Width = 50 mils

Gap=20.5 mils

I build this board and it turns out my transmission and reflection begins to deteriorate really bad after 6 GHz.

I also simulated this on a 3D EM simulator. This also shows both my S11 and S21 are poorly performing.

As a sanity check I made the trace thinner (down to 10 mil) and it significantly improved both S11 and S21.

Does anyone have any idea what I’m doing wrong?:?::?::?::?: