tim82518

Newbie

hey man

I am a beginner of PLL design. Here I have a problem about how to setup the .trannoise parameters to measure the jitter. Would anyone share your experience about the setup of trannoise? Thank you very much.

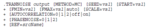

My PLL design has 200MHz output frequency. Following the format in hspice manual showing below, I'm curious about how to determine the value of "seed", "SCALE", "FMIN" and "FMAX".

About the FMAX, I have noticed that the manual suggest to 2*highest frequency of circuit. Why is that?

BR

CH

I am a beginner of PLL design. Here I have a problem about how to setup the .trannoise parameters to measure the jitter. Would anyone share your experience about the setup of trannoise? Thank you very much.

My PLL design has 200MHz output frequency. Following the format in hspice manual showing below, I'm curious about how to determine the value of "seed", "SCALE", "FMIN" and "FMAX".

About the FMAX, I have noticed that the manual suggest to 2*highest frequency of circuit. Why is that?

BR

CH