Khan2813

Newbie level 2

Hi

I am designing single stage Differential Drive CMOS cross coupled bridge Rectifer for Passive RFID using 65nm technology at 5.8GHz in Cadence. Now i wanted to observe the effect of reverse leakage current on my rectifier performance, how can i do that since i do not have any supply. Which simulation should i run?

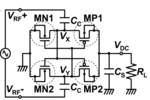

Attached file is the schematic of rectifier.

I am designing single stage Differential Drive CMOS cross coupled bridge Rectifer for Passive RFID using 65nm technology at 5.8GHz in Cadence. Now i wanted to observe the effect of reverse leakage current on my rectifier performance, how can i do that since i do not have any supply. Which simulation should i run?

Attached file is the schematic of rectifier.