promach

Advanced Member level 4

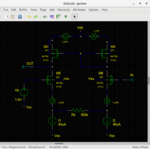

Do you guys have any idea how to select mosfet sizing of asymmetric differential pair for maximum output impedance ?

I have derived the Rout expression at https://www.eevblog.com/forum/begin...mall-signal-expression/msg1581412/#msg1581412

I have derived the Rout expression at https://www.eevblog.com/forum/begin...mall-signal-expression/msg1581412/#msg1581412