inass57

Member level 2

hi guys!

I have designed an LNA working at 9.35GHz with ADS using cosimulation. here is its layout:

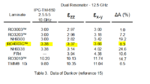

I have printed two of this LNA to compare to my simulation and i have a frequency shift, as shown in the picture below.

I have checked the substrate height, copper thickness but i have doubts about the permitivitty of the substrate (i'm using RO4003C) but i should mention that i didn't have those frequency shifts on my filters.

Any insight would be appreciated. thank you in advance.

I have designed an LNA working at 9.35GHz with ADS using cosimulation. here is its layout:

I have printed two of this LNA to compare to my simulation and i have a frequency shift, as shown in the picture below.

I have checked the substrate height, copper thickness but i have doubts about the permitivitty of the substrate (i'm using RO4003C) but i should mention that i didn't have those frequency shifts on my filters.

Any insight would be appreciated. thank you in advance.