Anklon

Member level 1

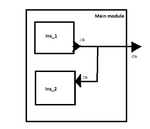

In my design, I have a clock generation block which generate main clock pulse ( no external clock reference is used like PLL ) . I'm facing problem defining sdc clock description.

I've tried; "create_clock" & "create_generated_clock" both command, but it fails to create any clock tree definition.

How can I approach to handle this situation?

I may have some misunderstanding about this whole thing and how to approach. Any example or source would be appreciable.

I've tried; "create_clock" & "create_generated_clock" both command, but it fails to create any clock tree definition.

**WARN: (IMPCCOPT-4144): The SDC clock func has source pin clk, which is an input pin. Clock trees for this clock will be defined under the corresponding output pins instead.

Type 'man IMPCCOPT-4144' for more detail.

Analyzing clock structure done.

Checking clock tree convergence...

Checking clock tree convergence done.

Placement constraints of type 'region' or 'fence' will not be downgraded to 'guide' because the property change_fences_to_guides has been set to false.

Set place::cacheFPlanSiteMark to 1

**ERROR: (IMPCCOPT-2004): Cannot run 'CCOpt' as no clock trees are defined.

**ERROR: (IMPCCOPT-2196): Cannot run ccopt_design because the command prerequisites were not met. Review the previous error messages for more details about the failure.

How can I approach to handle this situation?

I may have some misunderstanding about this whole thing and how to approach. Any example or source would be appreciable.