Martynas Jankūnas

Newbie level 6

Multilayer inductor parameter measurement with VNA

I made some multilayer inductors in standard CMOS process with variable inductance. Design principle is similar to this example :

Park, P.; et al. 2004. Variable Inductance Multilayer Inductor with MOSFET Switch Control, IEEE Electron Device Letters, vol. 25, 144–146.

In order to compensate parasitic elements I shorted two pads in the IC design. So my Idea for testing basically was to measure S11 (I have PocketVNA) of my inductor, convert to R and X, measure S11 of my short circuit in IC, convert to R and X, subtract one from another, because parasitic elements connected in series with inductors.

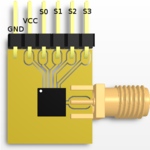

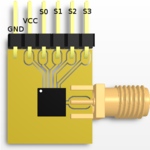

My one of test boards and measurement rig:

However I got results which are back to front e.g.:

each time I open one of control NMOS I get increased inductor resistance and bigger total inductance. In theory it should be opposite, NMOS channel is parallel connected to the part of inductor, at worst inductor resistance should stay similar than before, same with inductance. I measured inductor resistances with dumb multimeter and indeed i got smaller resistances each time I opened a NMOS transistors.

Either my VNA have not enough resolution and parasitic elements are too big compared with actual inductor or my measurement methodology is incorrect.

All advices how to properly measure inductor parameters (R, L, Q, fsr) are welcome.

PS. I tried to calibrate VNA through short circuited pads, but results were way off. I don't have access to better VNA.

I made some multilayer inductors in standard CMOS process with variable inductance. Design principle is similar to this example :

Park, P.; et al. 2004. Variable Inductance Multilayer Inductor with MOSFET Switch Control, IEEE Electron Device Letters, vol. 25, 144–146.

In order to compensate parasitic elements I shorted two pads in the IC design. So my Idea for testing basically was to measure S11 (I have PocketVNA) of my inductor, convert to R and X, measure S11 of my short circuit in IC, convert to R and X, subtract one from another, because parasitic elements connected in series with inductors.

My one of test boards and measurement rig:

However I got results which are back to front e.g.:

each time I open one of control NMOS I get increased inductor resistance and bigger total inductance. In theory it should be opposite, NMOS channel is parallel connected to the part of inductor, at worst inductor resistance should stay similar than before, same with inductance. I measured inductor resistances with dumb multimeter and indeed i got smaller resistances each time I opened a NMOS transistors.

Either my VNA have not enough resolution and parasitic elements are too big compared with actual inductor or my measurement methodology is incorrect.

All advices how to properly measure inductor parameters (R, L, Q, fsr) are welcome.

PS. I tried to calibrate VNA through short circuited pads, but results were way off. I don't have access to better VNA.