chandlerbing65nm

Member level 5

hi edaboards!

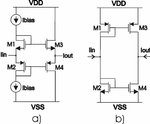

I have a simple question. In a current mirror in the attached photo. The drain current from transistor M1 is mirrored to transistor M3, but the drain current from M3 is not stable due to channel length modulation. My question is how can I make the drain current of the current mirror in transistor M3 stable or independent of the channel length modulation? Thank you for answering my question .

I have a simple question. In a current mirror in the attached photo. The drain current from transistor M1 is mirrored to transistor M3, but the drain current from M3 is not stable due to channel length modulation. My question is how can I make the drain current of the current mirror in transistor M3 stable or independent of the channel length modulation? Thank you for answering my question .