ggiacomo

Newbie level 3

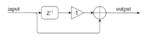

Hello. I need to implement a certain block in VHDL. The design would be something similar to this one.

At first it seemed very easy to me, but after looking into it I realised I am not sure about how to handle the delay. The design has to be synthesizable, so I cannot use "after".

I have tried a simple approach but Im not sure if thats allowed. Assuming one clock cycle delay, the process is

Would it be the correct approach or there is a different way?

At first it seemed very easy to me, but after looking into it I realised I am not sure about how to handle the delay. The design has to be synthesizable, so I cannot use "after".

I have tried a simple approach but Im not sure if thats allowed. Assuming one clock cycle delay, the process is

Code VHDL - [expand]

Would it be the correct approach or there is a different way?