chandlerbing65nm

Member level 5

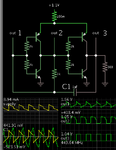

I've been working about this ramp generator circuit (attached file) for my research. Initially I want to have a ramp output of frequency 100MHz to 1GHz but I have a problem because i can only get 20-30kHz ramp signal. In my reference paper, the formula of frequency is f =Vref/(RtCt(Vh-Vl)) or f = Io/CV, but no matter what value I change the parameters(Vref, Ct, Rt and Schmitt trigger sizes) it still would not get a high frequency output, instead I only get a distorted output.

Here are the values of the parameters which I can get a clean ramp output but with small frequency:

Rt = 5k

Vref = 1V

Ct = 1nF

Vh = 0.7V

Vl = 0.25

Vdd = 1.2V

using the formula f =Vref/(RtCt(Vh-Vl)); f = 444.44kHz

but in my simulation output, I only get 32kHz ramp signal.

I use TSMC 65nm technology in my simulation.

I attached my reference paper in this study.

Please someone expert in these things, please I need help. Thank you!

Here are the values of the parameters which I can get a clean ramp output but with small frequency:

Rt = 5k

Vref = 1V

Ct = 1nF

Vh = 0.7V

Vl = 0.25

Vdd = 1.2V

using the formula f =Vref/(RtCt(Vh-Vl)); f = 444.44kHz

but in my simulation output, I only get 32kHz ramp signal.

I use TSMC 65nm technology in my simulation.

I attached my reference paper in this study.

Please someone expert in these things, please I need help. Thank you!