CataM

Advanced Member level 4

- Joined

- Dec 23, 2015

- Messages

- 1,275

- Helped

- 314

- Reputation

- 628

- Reaction score

- 312

- Trophy points

- 83

- Location

- Madrid, Spain

- Activity points

- 8,409

Hello everyone,

I have a PSFB converter done in PLECS from Plexim but I can not make it work, even though theoretically looks good.

I can not see any mistake in my implementation, so I need someone else to look at it.

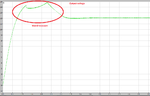

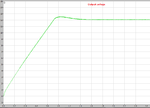

The problem is that the voltage feedback implemented by the Op-Amp is not regulating i.e. it sets the "control signal" for the CPM controller so high, that the current never reaches it and hence the SR flip flop never resets => never switches the bridge leg.

In other words, seems like the converter operates in "open loop".

OP Amp output --> scope 5, it is so high that it can not regulate the converter.

I simply can not see why it does not work.

Output voltage should be 12 V.

"Inverted Biflop" subsystem --> implements the dead time between MOSFETs in the same leg.

Find attached the PLECS schematic. If you need any additional information, just ask, I will kindly provide.

Any comment is highly appreciated !

I have a PSFB converter done in PLECS from Plexim but I can not make it work, even though theoretically looks good.

I can not see any mistake in my implementation, so I need someone else to look at it.

The problem is that the voltage feedback implemented by the Op-Amp is not regulating i.e. it sets the "control signal" for the CPM controller so high, that the current never reaches it and hence the SR flip flop never resets => never switches the bridge leg.

In other words, seems like the converter operates in "open loop".

OP Amp output --> scope 5, it is so high that it can not regulate the converter.

I simply can not see why it does not work.

Output voltage should be 12 V.

"Inverted Biflop" subsystem --> implements the dead time between MOSFETs in the same leg.

Find attached the PLECS schematic. If you need any additional information, just ask, I will kindly provide.

Any comment is highly appreciated !

Attachments

Last edited: