assemelgohari

Junior Member level 1

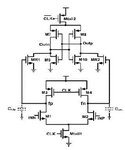

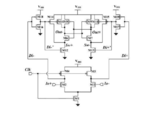

It's a sar adc for BLE receiver so it should be low power and its frequency is 10 MS/s, so was the comparator from this masters it was used for low power and same frequency.

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

where M2 & M3 dimensions are W= 1.2u 7 L =2u, and I tried a fast run of monte carlo of only 20 runs to see the range of voffset, maximum voffset was -5 mV. So I think using this circuit would be better, don't you ?

where M2 & M3 dimensions are W= 1.2u 7 L =2u, and I tried a fast run of monte carlo of only 20 runs to see the range of voffset, maximum voffset was -5 mV. So I think using this circuit would be better, don't you ? I think it is quite accurate and simple method to measure offset. And I don't know why you don't have Mismatch contribution in the drop-down menu. It should be under the 'Sensitivity results'. Are you sure you ticked the 'Save Mismatch Data' at the MC options?

If you want to save the signals under MC simulation you should tick the 'Save Data to Allow Family Plots'.

We don't know too much about your project to say yes you need an other comparator. We don't know the application, the speed, consumption limit, etc.