assemelgohari

Junior Member level 1

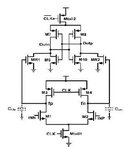

I have designed a comparator for an ADC and I want to measure its offset. All i know is to introduce a ramp voltage from 0 to Vref and on the other input a dc Vref/2 and the offset is the point at which the output switch from 0 to vdd. So I used a VPWL source and made to increase from two voltage points close to vref/2 as in the picture

. the output was as in this picture :

. the output was as in this picture :  .

.

My question is : Is this a valid way to measure the comparator's offset ??

Also if I would like to know its input capacitance, what should I do ?

. the output was as in this picture :

. the output was as in this picture :  .

. My question is : Is this a valid way to measure the comparator's offset ??

Also if I would like to know its input capacitance, what should I do ?