sakkano2

Newbie level 4

Hello.

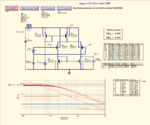

I need to design a single-phase Cmos op-amp as my homework.I try to design the circuit shown below and made calculations on it but when i simulate the circuit on LTSpice i get unwanted gain value.I try to make adjustements on Mosfet s to reach the desired gain of 20dB but i can not reach that value.Is there anything wrong with my circuit? and how can i reach 20dB gain. I will be very gratefull if you can help me.

My paramaters are;

Gain=20dB

Gain Bandwith = 1MHz

Supply Voltage = 2.5Volts

Power Budget=5mW

Load capacitance=100pF

I assume ICMR as -1 to 2 Volts , K'p =63uA , K'n=325uA , Vtp=-0.46V, Vtn=0.49.

With respect to these values i found W/L ratios and transconductance values.

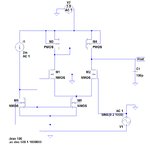

and my Spice file is:

Thank you very much for your help.

Have a Good Day.

I need to design a single-phase Cmos op-amp as my homework.I try to design the circuit shown below and made calculations on it but when i simulate the circuit on LTSpice i get unwanted gain value.I try to make adjustements on Mosfet s to reach the desired gain of 20dB but i can not reach that value.Is there anything wrong with my circuit? and how can i reach 20dB gain. I will be very gratefull if you can help me.

My paramaters are;

Gain=20dB

Gain Bandwith = 1MHz

Supply Voltage = 2.5Volts

Power Budget=5mW

Load capacitance=100pF

I assume ICMR as -1 to 2 Volts , K'p =63uA , K'n=325uA , Vtp=-0.46V, Vtn=0.49.

With respect to these values i found W/L ratios and transconductance values.

and my Spice file is:

Code dot - [expand]

Thank you very much for your help.

Have a Good Day.

Last edited by a moderator: