sakkano2

Newbie level 4

Hello everybody.

I need to desing a single-stage Cmos amplifier with following conditions.

Gain = 20 dB

Bandwidth = 1 MHz

Supply Voltage = 2.5 Volts

Power Budget = 5 mW

Load Capacitance = 100 pF

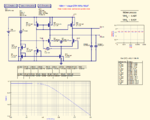

I made a research and i found the circuit below and made some calculations with respect to it.My question is, is there a simpler circuit design? and could you please help me with this design?

Thank you very much.

I need to desing a single-stage Cmos amplifier with following conditions.

Gain = 20 dB

Bandwidth = 1 MHz

Supply Voltage = 2.5 Volts

Power Budget = 5 mW

Load Capacitance = 100 pF

I made a research and i found the circuit below and made some calculations with respect to it.My question is, is there a simpler circuit design? and could you please help me with this design?

Thank you very much.