flote21

Advanced Member level 1

Hello folks!

I am working in a new design based on the Xilinx evaluation kit Zc702. I wanna preserve the most of the parts of the evaluation board but I need to attach to independent Ethernet PHY to the Processor Part. I ahve searching in internet and I did not found any info about it. And after reading the user manual of the evaluation kit (ug850-Zc702-eval-bd) I have a question at this point:

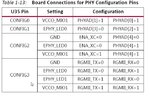

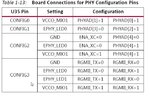

"On power-up, or on reset, the PHY is configured to operate in RGMII mode with PHY address 0b00111 using the settings shown in Table 1-13. These settings can be overwritten using software commands passed over the MDIO interface"

The question is: Which should be the configuration of the second Ethernet PHY to reach a proper individual working of both ethernet interfaces? What changes should I do in the schematics??

Thanks in advance.

I am working in a new design based on the Xilinx evaluation kit Zc702. I wanna preserve the most of the parts of the evaluation board but I need to attach to independent Ethernet PHY to the Processor Part. I ahve searching in internet and I did not found any info about it. And after reading the user manual of the evaluation kit (ug850-Zc702-eval-bd) I have a question at this point:

"On power-up, or on reset, the PHY is configured to operate in RGMII mode with PHY address 0b00111 using the settings shown in Table 1-13. These settings can be overwritten using software commands passed over the MDIO interface"

The question is: Which should be the configuration of the second Ethernet PHY to reach a proper individual working of both ethernet interfaces? What changes should I do in the schematics??

Thanks in advance.