ecasha

Junior Member level 2

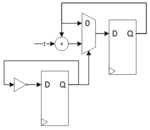

How to write verilog code such that output values should change for every 2 clock cycles? I have written code for counter,it is changing/counting for every posedge of clock.I want, it should count after 2 posedge clock .How do i write code?

Code:

always @ (posedge clk) begin

if (rst)

d<= 0;

else

d<=d+1;

end