viyaaloth

Junior Member level 3

Hi all,

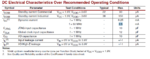

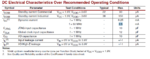

I am doing a custom design with Xilinx CPLD and xilinx FPGA. Now I am working with power requirements. I am using xilinx XC2C32A CPLD. I suppose to use 3.3V voltage as VCCIO and VCC=1.8V as voltage. But how can I get to know the maximum current rating for the corresponding voltages. What is meant by ICC(dynamic current) ?

Regards,

Viya

I am doing a custom design with Xilinx CPLD and xilinx FPGA. Now I am working with power requirements. I am using xilinx XC2C32A CPLD. I suppose to use 3.3V voltage as VCCIO and VCC=1.8V as voltage. But how can I get to know the maximum current rating for the corresponding voltages. What is meant by ICC(dynamic current) ?

Regards,

Viya