Vivek_2017

Newbie level 4

Hi,

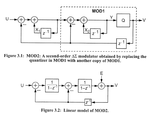

I am designing a discrete time integrator with transfer function = 1/(1-Z^-1) using model writer of the cadence virtuoso, below is the verilogA code of the integrator. But I am getting a gain of more than 1000 in the output, when applying an input signal of 900 uV (p-p).

I added the screenshot of the schematic as well as the transient output response of the integrator.

I am designing a discrete time integrator with transfer function = 1/(1-Z^-1) using model writer of the cadence virtuoso, below is the verilogA code of the integrator. But I am getting a gain of more than 1000 in the output, when applying an input signal of 900 uV (p-p).

I added the screenshot of the schematic as well as the transient output response of the integrator.

Code Verilog - [expand]

Last edited by a moderator: