Abhi3005

Newbie level 4

Very urgent.

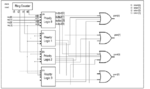

I would like know that how can we code a round robin arbiter using a ring counter for token generation means if the token is with first user first priority logic 0 will be enabled and so on.Based on the person who is accessing the resource the corresponding value of the person comes as output of priority encoder and will be decoded again in order to get corresponding grant signal.

The design contains :

ring counter for token generation at every posedge of clk which will enable priority logic.

priority logic contains priority encoder and a decoder .

4 request signals are there 4 grant signals at output.

please help me with the code, i am not getting the clear idea as i m a beginner.

I would like know that how can we code a round robin arbiter using a ring counter for token generation means if the token is with first user first priority logic 0 will be enabled and so on.Based on the person who is accessing the resource the corresponding value of the person comes as output of priority encoder and will be decoded again in order to get corresponding grant signal.

The design contains :

ring counter for token generation at every posedge of clk which will enable priority logic.

priority logic contains priority encoder and a decoder .

4 request signals are there 4 grant signals at output.

please help me with the code, i am not getting the clear idea as i m a beginner.