msdarvishi

Full Member level 4

Hello,

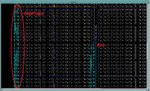

I have a question and I am wondering the best and easiest way to generate a code for a design that a group of 100 flip-flops are connected to only 1 node of the design? For example the net_1 in my design my be fanned out to 100 Dflip-flops ! Should I instantiate 100 flip flops in my VHDL code?

Kind replies are in advance appreciated !

Regards,

I have a question and I am wondering the best and easiest way to generate a code for a design that a group of 100 flip-flops are connected to only 1 node of the design? For example the net_1 in my design my be fanned out to 100 Dflip-flops ! Should I instantiate 100 flip flops in my VHDL code?

Kind replies are in advance appreciated !

Regards,