dpaul

Advanced Member level 5

Hello,

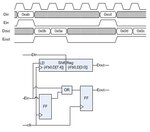

At a fixed clock rate, when an enable signal is high (at an interval of every 40ns), I have 8 bits data stream packs of the form (it is continuously being changed by the input source):

d5 5a 02 03 04 05 06

i.e. d5 is valid for 40ns, then 5a is valid for 40ns, and so on.

Now I want to convert this data stream in to the form:

05 0d 0a 05 02 00 03 00 04 00 05 00 06 00

Logically the split up would be that the LSB nibble of each 8 bits needs to be padded with "0000" and re transmitted as a separate 8 bit data. Then the MSB nibble of the same packet is to be padded with "0000" needs to be re-transmitted. That is to be repeated for all the incoming 8bit

1st split d5 --> 05 and then after 40ns d5 --> 0d. Then split 5a --> 0a and then 5a --> 05.

This split and transmission of the the new 8 bits should also happen when the same enable signal is high (at an interval of every 40ns). The clock will also remain the same.

What could be a clean and easy solution for this transformation.

At a fixed clock rate, when an enable signal is high (at an interval of every 40ns), I have 8 bits data stream packs of the form (it is continuously being changed by the input source):

d5 5a 02 03 04 05 06

i.e. d5 is valid for 40ns, then 5a is valid for 40ns, and so on.

Now I want to convert this data stream in to the form:

05 0d 0a 05 02 00 03 00 04 00 05 00 06 00

Logically the split up would be that the LSB nibble of each 8 bits needs to be padded with "0000" and re transmitted as a separate 8 bit data. Then the MSB nibble of the same packet is to be padded with "0000" needs to be re-transmitted. That is to be repeated for all the incoming 8bit

1st split d5 --> 05 and then after 40ns d5 --> 0d. Then split 5a --> 0a and then 5a --> 05.

This split and transmission of the the new 8 bits should also happen when the same enable signal is high (at an interval of every 40ns). The clock will also remain the same.

What could be a clean and easy solution for this transformation.