Terminator3

Advanced Member level 3

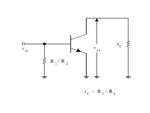

Assuming high frequency BJT (10GHz), where all biasing is done through high impedance thin lines with quarterwave stubs.

what would be equivalent circuit? R1,R2,Rc,Re only loaded by DC.

http://ecetutorials.com/analog-elec...tabilization-biasing-circuitsthermal-runaway/

Should i consider something like Rc=50 Ohm?

what would be equivalent circuit? R1,R2,Rc,Re only loaded by DC.

http://ecetutorials.com/analog-elec...tabilization-biasing-circuitsthermal-runaway/

Should i consider something like Rc=50 Ohm?