Terminator3

Advanced Member level 3

How to use Synthesizer PLL ICs with Integrated VCO to make harmonic VCO(6GHz->24Ghz)?

Hello all! I have recently seen some blurry photo of K-band VCO.

Most importantly, instead of traditional DRO/microstrip resonator or some kind of Hititte VCO chip, or some multi-stage multiplier there was something different:

i think it is some pretty damn simple yet cost effective 6GHz to 24GHz multiplier!

There is a pretty huge chip, i suspect something like LTC6946, LTC6948 (VCO+PLL). Also there is smaller chip, i think it is ATMEL or something to configure VCO+PLL chip.

1) VCO+PLL single chip (something around ~6GHz)

2) Some transition part to optimize x4 harmonics

3) Clearly it is 24GHz band-pass filter,

4,5) Two-stage amplifier to amplify 24GHz

6) Receiving antenna single-stage amplifier

7) Rat-race balanced mixer (schottky diodes)

I am pretty sure, that (1) chip is not 24GHz, and not even 12GHz. Although it may be 12GHz, but i still feel that it is something cheaper.

As you can see, two-stage amplifier (4,5) have no any filtering, so it is not multi-stage multiplier. The only band-pass filter is (3), and it is clearly final frequency here, just very weak before amplified.

Here is transition between some low-frequency chip (green part) and K-band part (white part):

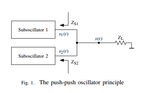

It is most important thing i want to understand in this design. There is two black chips, looks like diodes or transistors. It is unknown. PLL+VCO chips usually have balanced output, so I suspect here signal is summed up somehow, so balanced output x4 harmonic is in-phase.

Also it can be push-push VCO with PLL chip, but i still hope it is something more interesting

If you have any thoughts about this design, please comment! Thanks!

Hello all! I have recently seen some blurry photo of K-band VCO.

Most importantly, instead of traditional DRO/microstrip resonator or some kind of Hititte VCO chip, or some multi-stage multiplier there was something different:

i think it is some pretty damn simple yet cost effective 6GHz to 24GHz multiplier!

There is a pretty huge chip, i suspect something like LTC6946, LTC6948 (VCO+PLL). Also there is smaller chip, i think it is ATMEL or something to configure VCO+PLL chip.

1) VCO+PLL single chip (something around ~6GHz)

2) Some transition part to optimize x4 harmonics

3) Clearly it is 24GHz band-pass filter,

4,5) Two-stage amplifier to amplify 24GHz

6) Receiving antenna single-stage amplifier

7) Rat-race balanced mixer (schottky diodes)

I am pretty sure, that (1) chip is not 24GHz, and not even 12GHz. Although it may be 12GHz, but i still feel that it is something cheaper.

As you can see, two-stage amplifier (4,5) have no any filtering, so it is not multi-stage multiplier. The only band-pass filter is (3), and it is clearly final frequency here, just very weak before amplified.

Here is transition between some low-frequency chip (green part) and K-band part (white part):

It is most important thing i want to understand in this design. There is two black chips, looks like diodes or transistors. It is unknown. PLL+VCO chips usually have balanced output, so I suspect here signal is summed up somehow, so balanced output x4 harmonic is in-phase.

Also it can be push-push VCO with PLL chip, but i still hope it is something more interesting

If you have any thoughts about this design, please comment! Thanks!

Last edited: