mrln55

Junior Member level 2

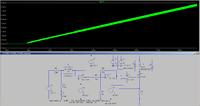

I have simulated an LT1793 op amp/IRF510 FET ramp generator with an inductive load and the simulation oscillates, but the phase magnitude plot doesn't seem to indicate a stability problem (see attached images). If C2 is increased to 1uF, the oscillation is suppressed in the simulation, but I would rather not have C2 in the circuit, since it allows some of the coil current to bypass R4. The circuit is intended to provide a 30 second ramp to a current of 20mA to 1.5 amps using various combinations of V2, R1, R2, and C1. Is there a compensation network that would improve the stability of this circuit or is there a better alternative for driving a coil?