micro7311

Junior Member level 2

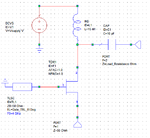

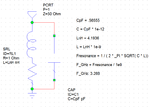

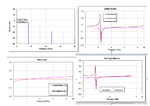

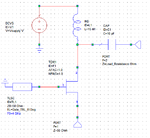

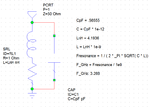

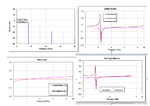

Hi, I am trying to simulate a reflection oscillator with a frequency of 4 GHz. Attached is my circuit and simulation plots. From what I understand from reflection oscillators, the resonator frequency is far below the oscillator output frequency. Here, my resonator frequency is ~3.268 GHz, which is not much below 4 GHz. Also, power output of the second harmonic is very close to the fundamental. The FET I am using is TOM1 model.

Could someone comment on this design and help optimize it? Thank you.

**broken link removed**

**broken link removed**

Could someone comment on this design and help optimize it? Thank you.

**broken link removed**

**broken link removed**