anhnha

Full Member level 6

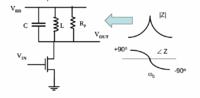

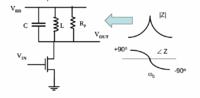

This is a tuned amplifier. I have two problems hope anyone here could make them clear.

1. As we know the output voltage swings above VDD. I can explain it from summing of DC and small signals.

However, is there a physics explanation for that? I mean using characteristic of R, L, C components.

2. For DC analysis, assuming that Vin and VDD are fixed and Vin is chosen so that the transistor is always in saturation.

(Vth < Vin < VDD + Vth)

Now from square law equation, the current Id from D to S should be constant and independent with shape ration W/L.

Is that right?

1. As we know the output voltage swings above VDD. I can explain it from summing of DC and small signals.

However, is there a physics explanation for that? I mean using characteristic of R, L, C components.

2. For DC analysis, assuming that Vin and VDD are fixed and Vin is chosen so that the transistor is always in saturation.

(Vth < Vin < VDD + Vth)

Now from square law equation, the current Id from D to S should be constant and independent with shape ration W/L.

Is that right?

Last edited by a moderator: