kidi3

Full Member level 1

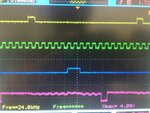

I tried testing it after changing the state of CS in the code. I then plugged it onto an oscilloscope, to see if the system also performed as I hoped it would do.. But from what i can read from the oscilloscope, The MOSI starts sending out a high bit, rather than sending 7 low bit and then 1 high. It looks like it is reversed?..

About

My plan was initially to shift each bit using this method, I was at that time confused on i should tell it to only do it, 7 time, or 10 times when i have to read data, and how exactly that operator worked.

About

Code:

shift_reg <= shift_reg(shift_reg'left -1 downto 0) & '0';My plan was initially to shift each bit using this method, I was at that time confused on i should tell it to only do it, 7 time, or 10 times when i have to read data, and how exactly that operator worked.