Shady Ahmed

Member level 5

I am designing a 3rd order sigma delta ADC with OSR = 32 , Fsampling = 64 MHz, with 1.5 bit comparator. The design is in 0.13um technology.

The target peak SNR from the system design (i used Schreier toolbox) was 76 dB.

After generating the system coefficients, i verified it on Cadence using ideal components.

The system peak SNR was 76 dB using Ideal op-amps (for the RC integrators), ideal feedback DAC & NON IDEAL (CMOS) comparator.

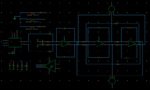

The system schematic showing the series of RC integrators, the feedback DAC & The comparator.

Now , i started designing the CMOS op amps, i have gone through several op amps trials however the system SNR degradation is HUGE, the best result i reached was 37 dB (instead of 76 dB for the ideal op amps)

1st op amp design trial:

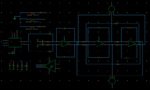

Schematic (i used a VCVS as the correction op amp in the CMFB , i'll replace it later if the op amp works)

The current in the second stage = 85 uA.

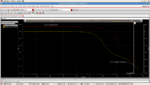

The op amp Bode Plots, since the sampling frequency = 64 MHz, the designed op amp GBW ~ 3 fs = 200 MHz, with Phase margin = 61 & DC gain = 46.7 dB

The CM bode plots & stability summary (generated using the stb analysis from the probe shown in the schematic)

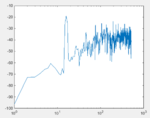

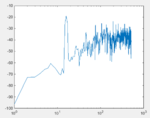

Finally , the PSD of the Sigma Delta ADC achieving ONLY 37 dB!!

I had a few other op amp trials with different GBW & DC gains, but i had no luck, 37 dB is the best result i got.

GBW , GAIN & Phase margin are the only design parameters i was thinking of while designing the op amp, am i missing something else? are there any other considerations i should take in the design?

Help me please and thanks for your time.

The target peak SNR from the system design (i used Schreier toolbox) was 76 dB.

After generating the system coefficients, i verified it on Cadence using ideal components.

The system peak SNR was 76 dB using Ideal op-amps (for the RC integrators), ideal feedback DAC & NON IDEAL (CMOS) comparator.

The system schematic showing the series of RC integrators, the feedback DAC & The comparator.

Now , i started designing the CMOS op amps, i have gone through several op amps trials however the system SNR degradation is HUGE, the best result i reached was 37 dB (instead of 76 dB for the ideal op amps)

1st op amp design trial:

Schematic (i used a VCVS as the correction op amp in the CMFB , i'll replace it later if the op amp works)

The current in the second stage = 85 uA.

The op amp Bode Plots, since the sampling frequency = 64 MHz, the designed op amp GBW ~ 3 fs = 200 MHz, with Phase margin = 61 & DC gain = 46.7 dB

The CM bode plots & stability summary (generated using the stb analysis from the probe shown in the schematic)

Finally , the PSD of the Sigma Delta ADC achieving ONLY 37 dB!!

I had a few other op amp trials with different GBW & DC gains, but i had no luck, 37 dB is the best result i got.

GBW , GAIN & Phase margin are the only design parameters i was thinking of while designing the op amp, am i missing something else? are there any other considerations i should take in the design?

Help me please and thanks for your time.

Last edited: