bowman1710

Full Member level 3

Hi guys,

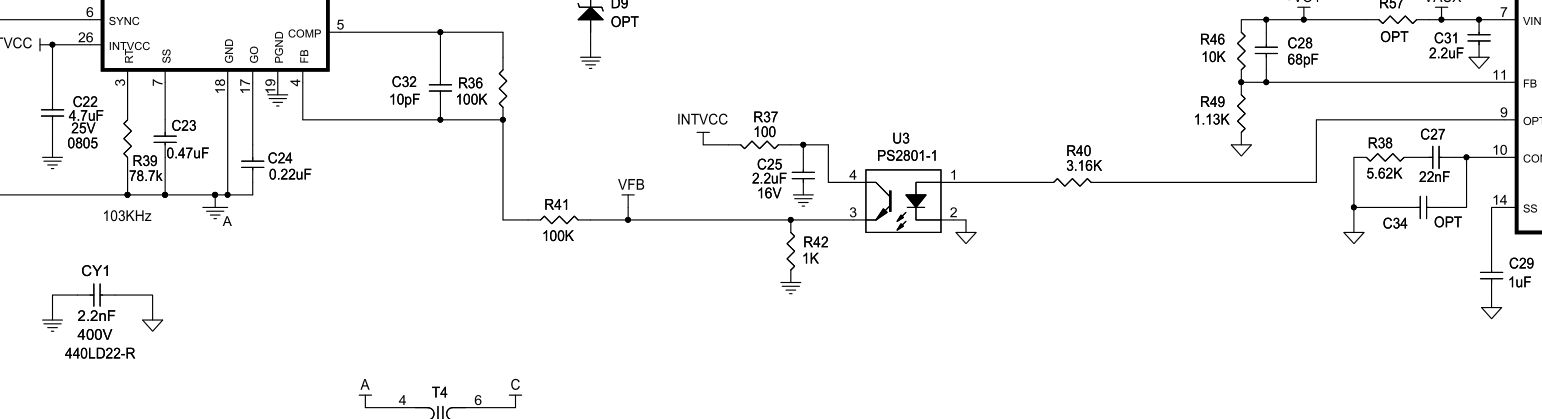

Having a small issue with my power supply design, its a 250-350V to 24V DC-DC forward converter, Basically I was having issues with jittering on my mosfet gate. I changed my compensation network values, this got rid of the jittering I was seeing but now when I increase the input voltage the output voltage decreases, is this because I have over compensated the loop?

Having a small issue with my power supply design, its a 250-350V to 24V DC-DC forward converter, Basically I was having issues with jittering on my mosfet gate. I changed my compensation network values, this got rid of the jittering I was seeing but now when I increase the input voltage the output voltage decreases, is this because I have over compensated the loop?