beginner_EDA

Full Member level 4

Hello everybody,

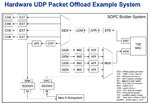

I have implemented UDP offload example

**broken link removed**

in DE2-115 FPGA board.

FPGA to PC data transfer seems to be working which I observed via Wireshark.

but for reverse direction (PC to FPGA), I got stuck.

I want to test the reverse direction (PC to FPGA) by sending some test data from PC.

I would like to know:

For test purpose can Hyperterminal/Putty be used to send data from PC to FPGA via Ethernet Interface ? Do I need some additional setting?

OR

Is there any other alternative?

Regards

I have implemented UDP offload example

**broken link removed**

in DE2-115 FPGA board.

FPGA to PC data transfer seems to be working which I observed via Wireshark.

but for reverse direction (PC to FPGA), I got stuck.

I want to test the reverse direction (PC to FPGA) by sending some test data from PC.

I would like to know:

For test purpose can Hyperterminal/Putty be used to send data from PC to FPGA via Ethernet Interface ? Do I need some additional setting?

OR

Is there any other alternative?

Regards