Hatmpatn

Member level 3

Good evening all edaboarders!

I've been given a task where I should calculate some values in an amplifier. I have under some time now gathered some knowledge in the electronics area, but not sufficient to solve this problem on my own. I was wondering if you could help me and point me in the right direction, calculations-wise!

Thanks in advance!

The problem:

----------------------------------------------

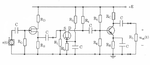

The amplifier has a common-drain amplifier at the input, followed by a common-gate amplifier and finally a common-emitter amplifier on the output.

The values for the resistors are: RD: 2kΩ RS: 15kΩ RG: 1MΩ R2: 16kΩ R5: 40kΩ R6: 10kΩ RC: 3kΩ RE: 2kΩ RL: 2kΩ E=12V

The parameters of the FET-transistors:

Up: -3.5V IDSS: 9mA Slope: 4mS exiting-admittance: 10µS Zin= ∞

This applies to the FET-transistors: iD=IDSS*(1-uGS/Up)²

The parameters of the bipolar transistor:

In-impedance: 1.5kΩ Feedback ratio: 2*10^-4 Current amplification factor: 100 Out-impedance: 50µS. B=100

These are the tasks of the problem:

a) Calculate R1, R3 and R4 so that the FET-transistors in the common-gate amplifier gets the operating point IDQ= 4mA, UDSQ= 2V and the gatepotential +2V.

b) Draw an equivalent small-signal schedule for the amplifierm where the FET-transistor's out-admittance and the bipolar transistor's feedback ratio and out-admittance are neglected. The capacitances are great.

Then calculate the out-voltage uout(t) if e(t)=sin(10³t) [mV].

-------------------------------------------------------------------

**Note that I'm not certain of these equivalent words in english which I have translated from swedish.

I've been given a task where I should calculate some values in an amplifier. I have under some time now gathered some knowledge in the electronics area, but not sufficient to solve this problem on my own. I was wondering if you could help me and point me in the right direction, calculations-wise!

Thanks in advance!

The problem:

----------------------------------------------

The amplifier has a common-drain amplifier at the input, followed by a common-gate amplifier and finally a common-emitter amplifier on the output.

The values for the resistors are: RD: 2kΩ RS: 15kΩ RG: 1MΩ R2: 16kΩ R5: 40kΩ R6: 10kΩ RC: 3kΩ RE: 2kΩ RL: 2kΩ E=12V

The parameters of the FET-transistors:

Up: -3.5V IDSS: 9mA Slope: 4mS exiting-admittance: 10µS Zin= ∞

This applies to the FET-transistors: iD=IDSS*(1-uGS/Up)²

The parameters of the bipolar transistor:

In-impedance: 1.5kΩ Feedback ratio: 2*10^-4 Current amplification factor: 100 Out-impedance: 50µS. B=100

These are the tasks of the problem:

a) Calculate R1, R3 and R4 so that the FET-transistors in the common-gate amplifier gets the operating point IDQ= 4mA, UDSQ= 2V and the gatepotential +2V.

b) Draw an equivalent small-signal schedule for the amplifierm where the FET-transistor's out-admittance and the bipolar transistor's feedback ratio and out-admittance are neglected. The capacitances are great.

Then calculate the out-voltage uout(t) if e(t)=sin(10³t) [mV].

-------------------------------------------------------------------

**Note that I'm not certain of these equivalent words in english which I have translated from swedish.