martin_t

Newbie level 6

- Joined

- Dec 23, 2013

- Messages

- 11

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Location

- Buenos Aires, Argentina

- Activity points

- 113

Hello guys.

This is my first post here, though I've been going trough the forum for rather some time.

I´m designing an inverter based around a dsPIC33FJ128MC802 and two IR2110 in a full bridge configuration driving four IRGP4063D IGBTs.

The PWM signal is switching at 20khz and the DC Bus voltage is 40Vdc, and the AC output is 220 Vac 50hz through a step up transformer and capacitor in parallel.

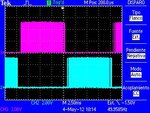

The thing is that as long as there's no load, the gates' waveforms are fine. But when I hook up the transformer, the signals that belong to the high side of both IR2110s star to behave in a strange way.

As you can see, there is some kind of modulation issue.

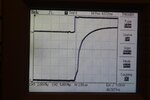

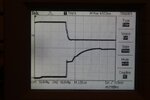

The strange thing is that I replaced two IGBTs from one of the two IR2110s for two MOSFETS, and the problem is gone. While on the other IR2110 I still have the same problem on the high side gate.

This is how the high side MOSFET behaves.

Is this a layout problem (PCB stray inductance)? I know IGBTs have the "tail current" problem, but is this how they are supposed to work?

Any help or comment will be much appreciated.

Thanks very much in advance and happy new year!!

Martín

This is my first post here, though I've been going trough the forum for rather some time.

I´m designing an inverter based around a dsPIC33FJ128MC802 and two IR2110 in a full bridge configuration driving four IRGP4063D IGBTs.

The PWM signal is switching at 20khz and the DC Bus voltage is 40Vdc, and the AC output is 220 Vac 50hz through a step up transformer and capacitor in parallel.

The thing is that as long as there's no load, the gates' waveforms are fine. But when I hook up the transformer, the signals that belong to the high side of both IR2110s star to behave in a strange way.

As you can see, there is some kind of modulation issue.

The strange thing is that I replaced two IGBTs from one of the two IR2110s for two MOSFETS, and the problem is gone. While on the other IR2110 I still have the same problem on the high side gate.

This is how the high side MOSFET behaves.

Is this a layout problem (PCB stray inductance)? I know IGBTs have the "tail current" problem, but is this how they are supposed to work?

Any help or comment will be much appreciated.

Thanks very much in advance and happy new year!!

Martín