slyfth

Junior Member level 2

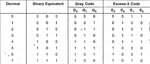

Hi fellow professionals/students, this is my first post here on eda. I am stuck at a place where I have no idea on how to proceed.

The problem is that I have to design a gray code to excess-3 converter using only NAND (IC 7000) gates. If someone can guide me on how to proceed, it'll be really helpful. Thanks in advance.

Regards

The problem is that I have to design a gray code to excess-3 converter using only NAND (IC 7000) gates. If someone can guide me on how to proceed, it'll be really helpful. Thanks in advance.

Regards