yhatagishi

Junior Member level 3

Hello all,

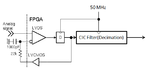

I want to realize delta-sigma ADC using FPGA, where digital processing (the cic filter) is implemented in FPGA and only R and C are the analog parts.

LVDS is used as comparator.

The block diagram is below.

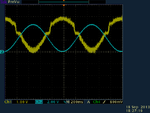

The problem is that the ADC ouput is not what I expect.

- when voltage of inputs are below 0.5 V : output is 0 V

- when voltage of inputs are near 2.5 V : output seems to be saturated around 2 V

When they are in 0.5 - 2.0 V and above 2.7 V, the output seems fine.

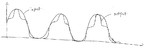

I drew the simple diagram of the input and output (Sorry for my bad drawing).

I am pretty sure that cic filter is working fine.

I think LVDS is the one causing those problems for the voltage that causes problems is outside the common mode voltage.

But I do not know how to deal with it...

So I want to know how I can solve those problems.

Or if anyone knows what the real problem is, please tell me.

Best regards,

Yukihiro Hatagishi

I want to realize delta-sigma ADC using FPGA, where digital processing (the cic filter) is implemented in FPGA and only R and C are the analog parts.

LVDS is used as comparator.

The block diagram is below.

The problem is that the ADC ouput is not what I expect.

- when voltage of inputs are below 0.5 V : output is 0 V

- when voltage of inputs are near 2.5 V : output seems to be saturated around 2 V

When they are in 0.5 - 2.0 V and above 2.7 V, the output seems fine.

I drew the simple diagram of the input and output (Sorry for my bad drawing).

I am pretty sure that cic filter is working fine.

I think LVDS is the one causing those problems for the voltage that causes problems is outside the common mode voltage.

But I do not know how to deal with it...

So I want to know how I can solve those problems.

Or if anyone knows what the real problem is, please tell me.

Best regards,

Yukihiro Hatagishi

Last edited: