kabaleevisu

Advanced Member level 2

- Joined

- Apr 14, 2010

- Messages

- 616

- Helped

- 85

- Reputation

- 170

- Reaction score

- 81

- Trophy points

- 1,308

- Location

- Chennai,India

- Activity points

- 4,512

Hi siva

Thanks for your reply

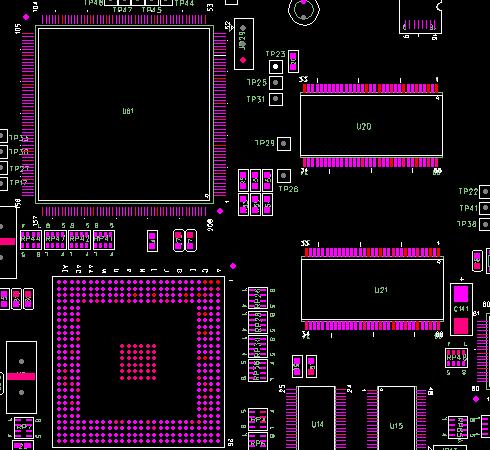

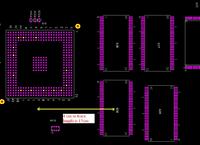

i have some queries below i am mention,still i am not complete my placement (i have some reference layout)

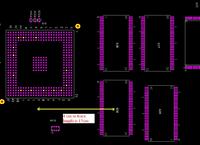

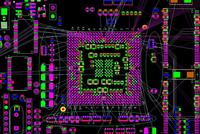

1.from MCF548x ColdFire® Microprocessor to DDR SDRAM Distance need to maintain is 4cm is it right?? or trace length should be 15cm or <6 inch right ? check the diagram

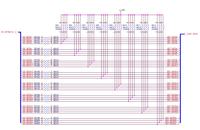

2.how to do the length match ?(i heard as per the DQS signal length i need to match the data signal right?

3.how to match the address signal??

Thanks for your reply

i have some queries below i am mention,still i am not complete my placement (i have some reference layout)

1.from MCF548x ColdFire® Microprocessor to DDR SDRAM Distance need to maintain is 4cm is it right?? or trace length should be 15cm or <6 inch right ? check the diagram

2.how to do the length match ?(i heard as per the DQS signal length i need to match the data signal right?

3.how to match the address signal??