bcro

Newbie level 6

Estimating Attenuation for Low Pass Filter in ADC->DAC System (am i doing it right?)

Hello All--

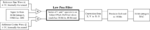

I'm learning DSP as I go while trying to implement a Lock-In Amplifier on an FPGA. Given the situation illustrated in the attached diagram, is it reasonable to say that the filter stop-band attenuation should be sufficient to reduce a full amplitude signal at the 16-bit ADC to one half the step size of the 16-bit DAC? In other words:

Minimum Atten. = 10*log(0.5*DAC-step / ADC-Range) = 10*log(0.5 / 65536) = -51.2dB

I know there are rounding and fixed-point noise considerations within the system, but I've not yet learned how I should or should not factor those into my high-level filter specs. In short, I could use some advice. Thanks in advance for the help.

--Brad

Hello All--

I'm learning DSP as I go while trying to implement a Lock-In Amplifier on an FPGA. Given the situation illustrated in the attached diagram, is it reasonable to say that the filter stop-band attenuation should be sufficient to reduce a full amplitude signal at the 16-bit ADC to one half the step size of the 16-bit DAC? In other words:

Minimum Atten. = 10*log(0.5*DAC-step / ADC-Range) = 10*log(0.5 / 65536) = -51.2dB

I know there are rounding and fixed-point noise considerations within the system, but I've not yet learned how I should or should not factor those into my high-level filter specs. In short, I could use some advice. Thanks in advance for the help.

--Brad