nana_7488

Member level 1

Hi all

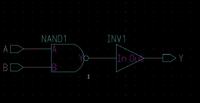

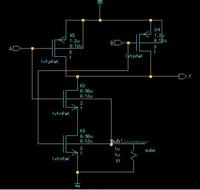

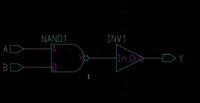

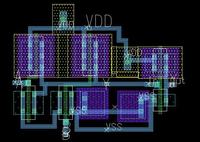

I have a problem with my LVS, it showing missing net in layout and schematic. I've view the netlist between layout and schematic, and it have difference net on the bulk connection of nfet;

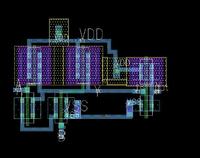

This is my layout netlist

M0 Y A 2 7 lvtnfet w=9.6e-07 l=1.2e-07 m=1 par=1 nf=1 ngcon=1 $X=-2460 $Y=16770 $D=21

M1 VSS B 7 sub! lvtnfet w=9.6e-07 l=1.2e-07 m=1 par=1 nf=1 ngcon=1 $X=-930 $Y=16770 $D=21

M2 Y A VDD VDD lvtpfet w=1.2e-06 l=1.2e-07 m=1 par=1 nf=1 ngcon=1 $X=-2150 $Y=18600 $D=101

M3 Y B VDD VDD lvtpfet w=1.2e-06 l=1.2e-07 m=1 par=1 nf=1 ngcon=1 $X=70 $Y=18600 $D=101

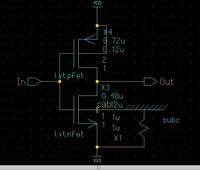

and this is my schematic netlist

M_X3 N$5 B VSS sub! lvtnfet w=0.96u l=0.12u m=2 nf=1 ngcon=1 par=2

M_X5 Y A VDD VDD lvtpfet w=1.2u l=0.12u m=3 nf=1 ngcon=1 par=3

M_X2 Y A N$5 sub! lvtnfet w=0.96u l=0.12u m=2 nf=1 ngcon=1 par=2

M_X4 Y B VDD VDD lvtpfet w=1.2u l=0.12u m=3 nf=1 ngcon=1 par=3

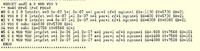

This are my LVS error

LAYOUT NAME SOURCE NAME

Discrepancy #1 in nand

Net 7 ** no similar net **

Discrepancy #2 in nand

** no similar net ** sub!

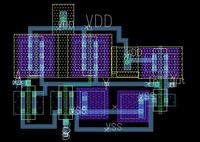

For your information, I didnt use subc device in my schematic, but name pull out wire from the bulk as sub!, and I've used ntiedown as substrate contact.

Can anyone tell me why is the netlist difference and how to solve this?I'm really stucked with this...Thanks

I have a problem with my LVS, it showing missing net in layout and schematic. I've view the netlist between layout and schematic, and it have difference net on the bulk connection of nfet;

This is my layout netlist

M0 Y A 2 7 lvtnfet w=9.6e-07 l=1.2e-07 m=1 par=1 nf=1 ngcon=1 $X=-2460 $Y=16770 $D=21

M1 VSS B 7 sub! lvtnfet w=9.6e-07 l=1.2e-07 m=1 par=1 nf=1 ngcon=1 $X=-930 $Y=16770 $D=21

M2 Y A VDD VDD lvtpfet w=1.2e-06 l=1.2e-07 m=1 par=1 nf=1 ngcon=1 $X=-2150 $Y=18600 $D=101

M3 Y B VDD VDD lvtpfet w=1.2e-06 l=1.2e-07 m=1 par=1 nf=1 ngcon=1 $X=70 $Y=18600 $D=101

and this is my schematic netlist

M_X3 N$5 B VSS sub! lvtnfet w=0.96u l=0.12u m=2 nf=1 ngcon=1 par=2

M_X5 Y A VDD VDD lvtpfet w=1.2u l=0.12u m=3 nf=1 ngcon=1 par=3

M_X2 Y A N$5 sub! lvtnfet w=0.96u l=0.12u m=2 nf=1 ngcon=1 par=2

M_X4 Y B VDD VDD lvtpfet w=1.2u l=0.12u m=3 nf=1 ngcon=1 par=3

This are my LVS error

LAYOUT NAME SOURCE NAME

Discrepancy #1 in nand

Net 7 ** no similar net **

Discrepancy #2 in nand

** no similar net ** sub!

For your information, I didnt use subc device in my schematic, but name pull out wire from the bulk as sub!, and I've used ntiedown as substrate contact.

Can anyone tell me why is the netlist difference and how to solve this?I'm really stucked with this...Thanks