sharezhao

Junior Member level 1

Dear all:

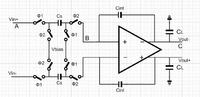

The switched capacitor integrator is as following. how to test the linearity of the integrator? I am considering to do it in following way.

1) Input is a pure sin wave, the do pss+pac, then calculate the iip3

2) input is a pure sin wave, the output is a stair-case sin wave, then sample the output and do DFT the watch the HD3.

Which way is better? Anyone watch this post must leave you idea. LoL!!

Thank you for your attention!!!

The switched capacitor integrator is as following. how to test the linearity of the integrator? I am considering to do it in following way.

1) Input is a pure sin wave, the do pss+pac, then calculate the iip3

2) input is a pure sin wave, the output is a stair-case sin wave, then sample the output and do DFT the watch the HD3.

Which way is better? Anyone watch this post must leave you idea. LoL!!

Thank you for your attention!!!