turtlewang

Member level 2

Hello everybody,

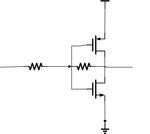

I want to convert a sine wave clock signal to a square wave clock. The sine wave is a clock signal generated from off-chip signal generator. It is frequency is 2.5GHz, it's peak to peak value is 100mV. I want to design a circuit to convert this clock signal to a square wave with rail to rail. Then I will use this square wave to clock my CMOS circuit.

My process node is TSMC 0.18um.

Does anybody know what is the common architecture for this purpose?

Can anybody recommend me some materials?

Thanks in advance!

I want to convert a sine wave clock signal to a square wave clock. The sine wave is a clock signal generated from off-chip signal generator. It is frequency is 2.5GHz, it's peak to peak value is 100mV. I want to design a circuit to convert this clock signal to a square wave with rail to rail. Then I will use this square wave to clock my CMOS circuit.

My process node is TSMC 0.18um.

Does anybody know what is the common architecture for this purpose?

Can anybody recommend me some materials?

Thanks in advance!