palmeiras

Full Member level 6

- Joined

- Feb 22, 2010

- Messages

- 375

- Helped

- 61

- Reputation

- 122

- Reaction score

- 50

- Trophy points

- 1,308

- Location

- South America

- Activity points

- 4,199

Hi everyone,

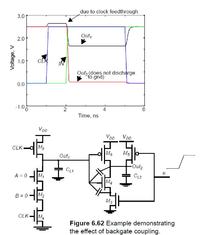

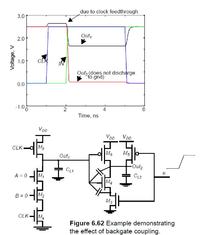

In the chapter 6, of (Jan M. Rabaey), he explains the “backategate coupling”.

This effect is shown in the attached figure.

Please, could someone explain why Cout2 does not go to exact gnd – when “in” goes from zero to 1? The figure shows that it Is not possible to completely discharge capacitor CL2.

Thank you,

Regards,

In the chapter 6, of (Jan M. Rabaey), he explains the “backategate coupling”.

This effect is shown in the attached figure.

Please, could someone explain why Cout2 does not go to exact gnd – when “in” goes from zero to 1? The figure shows that it Is not possible to completely discharge capacitor CL2.

Thank you,

Regards,