LvW

Advanced Member level 6

I just used a standard two-stage OP (p-input pairs).

Please, tell us about your "standard two-stage OP".

Did you create your own model? Is it a manufacturer model? Which type?

Which parameters: open-loop gain, input/output impedances?

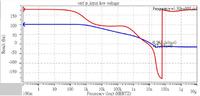

In particular, the output impedance seems to be "critical". Otherwise I have no explanation for the output voltage that shows NO continuous reduction for rising frequencies (as shown in one of the earlier diagrams).