alkaios

Newbie level 5

hello

I want to ask: does shift arithmetic always creates latches in vhdl?

Is there any way to prevent this from happening?

Should I or should I not care about these latches?

Here's my code:

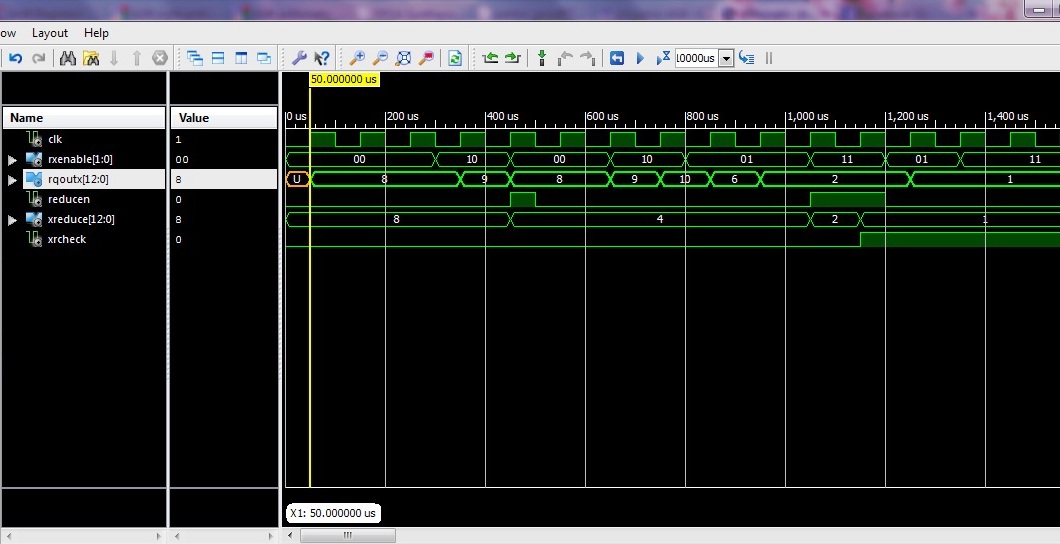

In the second process, i do the sra in the signal xreduce.

I used the shreg_extract constraint, because i thought it would help.

Is my code correct?

here are the warnings that XST produces:

Thanks in advance

I want to ask: does shift arithmetic always creates latches in vhdl?

Is there any way to prevent this from happening?

Should I or should I not care about these latches?

Here's my code:

Code VHDL - [expand]

In the second process, i do the sra in the signal xreduce.

I used the shreg_extract constraint, because i thought it would help.

Is my code correct?

here are the warnings that XST produces:

Code VHDL - [expand]

Thanks in advance

Last edited: