khaled2k

Member level 2

Dear fellows,

I am designing a CMOS Dickson charge pump. The charge pump works fine when using ideal non-overlapping clock sources (vdc from analogLib).

The problem arises when using a clock oscillator (or even an ideal source) and apply it to a circuit to generate the 2 non-overlapping clocks.

When testing the clock generation circuit alone, it generates the clocks fine.

The charge pump with ideal sources is fine too.

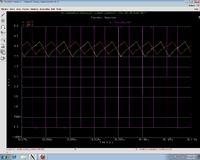

When apply the clock source to clock generation circuit then its output to the charge pump, the clocks (clk1, clk2) output is like shown in figure

I am sure that the clock circuit works fine as a unit and the charge pump as well. The problem when connecting them together.

Thanks in advance

I am designing a CMOS Dickson charge pump. The charge pump works fine when using ideal non-overlapping clock sources (vdc from analogLib).

The problem arises when using a clock oscillator (or even an ideal source) and apply it to a circuit to generate the 2 non-overlapping clocks.

When testing the clock generation circuit alone, it generates the clocks fine.

The charge pump with ideal sources is fine too.

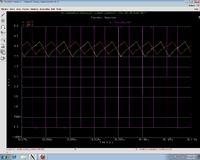

When apply the clock source to clock generation circuit then its output to the charge pump, the clocks (clk1, clk2) output is like shown in figure

I am sure that the clock circuit works fine as a unit and the charge pump as well. The problem when connecting them together.

Thanks in advance