niranjan1984

Newbie level 6

Hi

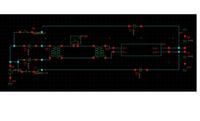

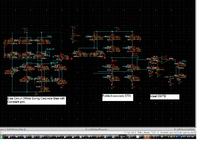

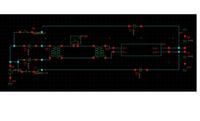

I have designed capacitive feedback fully differentail OTA. I am trying to simulate loop gain and step response of OTA. Fig1 shows the test bench used

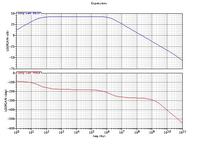

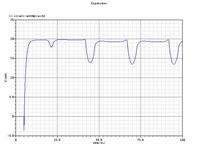

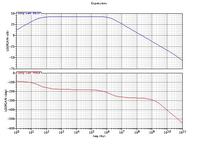

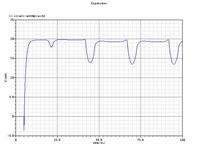

Fig2 shows the loop gain and fig3 shows the step response. I have following questions

1. Why loop gain curve is not flat at the beginning? Theory shows that at low frequency loop gain equals to T0=β.Gm.Ro and hence should be flat

2. Why is the step response showing these humps? Is this because of loop gain issue? or something else

I am not getting this please help.

Thanks

I have designed capacitive feedback fully differentail OTA. I am trying to simulate loop gain and step response of OTA. Fig1 shows the test bench used

Fig2 shows the loop gain and fig3 shows the step response. I have following questions

1. Why loop gain curve is not flat at the beginning? Theory shows that at low frequency loop gain equals to T0=β.Gm.Ro and hence should be flat

2. Why is the step response showing these humps? Is this because of loop gain issue? or something else

I am not getting this please help.

Thanks